# **CMOS linear image sensor**

S12443

Pixel size:  $7 \times 125 \mu m$ , 2496 pixels, small package

The S12443 is a CMOS linear image sensor with a compact yet 2496-pixel long photosensitive area (effective photosensitive area length: 17.472 mm). The pixel size is 7  $\times$  125  $\mu m.$

### Features

- Pixel size: 7 × 125 μm

- 2496 pixels

- **■** Effective photosensitive area length: 17.472 mm

- 3.3 V single power supply operation

- Built-in timing generator allows operation with only start and clock pulse inputs.

- Video data rate: 10 MHz max.

- Small input terminal capacitance: 5 pF

# Applications

- **■** Barcode readers

- Position detection

- **■** Image reading

- Encoders

#### Structure

| Parameter                  | Specification  | Unit |

|----------------------------|----------------|------|

| Number of pixels           | 2496           | -    |

| Pixel pitch                | 7              | μm   |

| Pixel height               | 125            | μm   |

| Photosensitive area length | 17.472         | mm   |

| Package                    | Glass epoxy    | -    |

| Seal material              | Silicone resin | -    |

# - Absolute maximum ratings

| Parameter                     | Symbol | Condition | Value                                      | Unit |

|-------------------------------|--------|-----------|--------------------------------------------|------|

| Supply voltage                | Vdd    | Ta=25 °C  | -0.3 to +6                                 | V    |

| Clock pulse voltage           | V(CLK) | Ta=25 °C  | -0.3 to +6                                 | V    |

| Start pulse voltage           | V(ST)  | Ta=25 °C  | -0.3 to +6                                 | V    |

| Operating temperature*1       | Topr   |           | -40 to +85                                 | °C   |

| Storage temperature*1         | Tstg   |           | -40 to +85                                 | °C   |

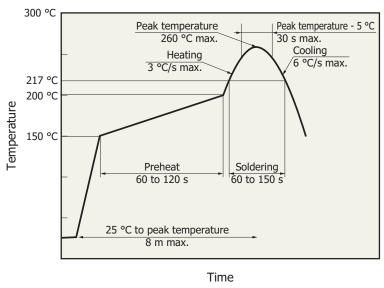

| Reflow soldering conditions*2 | Tsol   |           | Peak temperature 260 °C, 3 times (see P.9) | -    |

Note: Exceeding the absolute maximum ratings even momentarily may cause a drop in product quality. Always be sure to the product within the absolute maximum ratings.

\*1: No condensation

\*2: JEDEC level 2a

### **➡** Recommended terminal voltage (Ta=25 °C)

| Parameter           |            | Symbol | Min. | Тур. | Max.       | Unit |

|---------------------|------------|--------|------|------|------------|------|

| Supply voltage      |            | Vdd    | 3.15 | 3.3  | 3.45       | V    |

| Clock pulse veltage | High level | V(CLK) | 3    | Vdd  | Vdd + 0.25 | V    |

| Clock pulse voltage | Low level  |        | 0    | -    | 0.3        | V    |

| Start pulse voltage | High level | V/(CT) | 3    | Vdd  | Vdd + 0.25 | V    |

|                     | Low level  | V(ST)  | 0    | -    | 0.3        | V    |

# **Input terminal capacitance (Ta=25 °C, Vdd=3.3 V)**

| Parameter                              | Symbol | Min. | Тур. | Max. | Unit |

|----------------------------------------|--------|------|------|------|------|

| Clock pulse input terminal capacitance | C(CLK) | -    | 5    | -    | pF   |

| Start pulse input terminal capacitance | C(ST)  | -    | 5    | -    | pF   |

# **■** Electrical characterisitics [Ta=25 °C, Vdd=3.3 V, V(CLK)=V(ST)=3.3 V]

| Parameter                | Symbol | Min.  | Тур.   | Max. | Unit |

|--------------------------|--------|-------|--------|------|------|

| Clock pulse frequency    | f(CLK) | 200 k | 5 M    | 10 M | Hz   |

| Video data rate          | VR     | -     | f(CLK) | -    | Hz   |

| Output impedance         | Zo     | 70    | -      | 260  | Ω    |

| Current consumption*3 *4 | I      | 14    | 21     | 30   | mA   |

<sup>\*3:</sup> f(CLK)=10 MHz

# **■** Electrical and optical characterisitics [Ta=25 °C, Vdd=3.3 V, V(CLK)=V(ST)=3.3V, f(CLK)=10 MHz]

| Parameter                         | Symbol | Min. | Тур.        | Max. | Unit              |

|-----------------------------------|--------|------|-------------|------|-------------------|

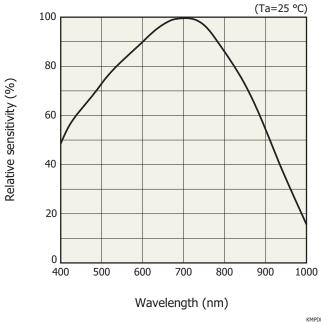

| Spectral response range           | λ      |      | 400 to 1000 |      | nm                |

| Peak sensitivity wavelength       | λр     | -    | 700         | -    | nm                |

| Photosensitivity*5                | R      | -    | 500         | -    | V/( <i>lx</i> ⋅s) |

| Conversion efficiency*6           | CE     | -    | 25          | -    | μV/e⁻             |

| Dark output voltage*7 *8          | Vd     | 0    | 0.4         | 4.0  | mV                |

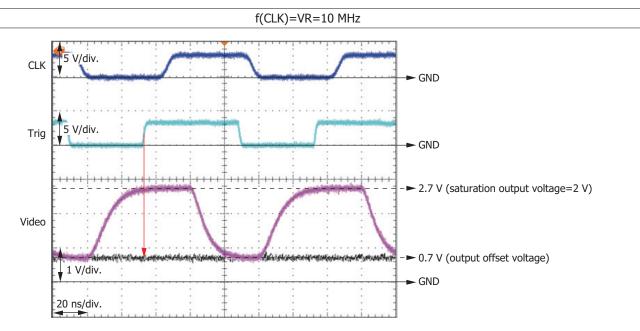

| Saturation output voltage*8       | Vsat   | 1.5  | 2.0         | 2.8  | V                 |

| Readout noise                     | Nr     | 0.9  | 1.2         | 2.0  | mV rms            |

| Dynamic range 1*9                 | DR1    | -    | 1666        | -    | times             |

| Dynamic range 2*10                | DR2    | -    | 5000        | -    | times             |

| Output offset voltage             | Vo     | 0.4  | 0.7         | 1.0  | V                 |

| Photoresponse nonuniformity*5 *11 | PRNU   | -    | -           | ±10  | %                 |

| Image lag*12                      | IL     | -    | -           | 0.1  | %                 |

<sup>\*5:</sup> Measured with a tungsten lamp of 2856 K

Integration time=10 ms

Dark output voltage is proportional to the integration time and so the shorter the integration time, the wider the dynamic range.

\*11: Photoresponse nonuniformity (PRNU) is the output nonuniformity that occurs when the entire photosensitive area is uniformly illuminated by light which is 50% of the saturation exposure level. PRNU is measured using 2490 pixels excluding 3 pixels each at both ends, and is defined as follows:  $PRNU = \Delta X/X \times 100$  (%)

X: average output of all pixels,  $\Delta X$ : difference between X and maximum output or minimum output

\*12: Signal components of the preceding line data that still remain even after the data is read out in a saturation output state. Image lag increases when the output exceeds the saturation output voltage.

<sup>\*4:</sup> Current consumption increases as the clock pulse frequency increases. The current consumption is 8 mA typ. at f(CLK)=200 kHz.

<sup>\*6:</sup> Output voltage generated per one electron

<sup>\*7:</sup> Integration time=10 ms

<sup>\*8:</sup> Difference from Vo

<sup>\*9:</sup> DR1 = Vsat/Nr

<sup>\*10:</sup> DR2 = Vsat/Vd

# **→** Appearance inspection standards

| Parameter                             | Test criterion | Inspection method |

|---------------------------------------|----------------|-------------------|

| Foreign matter on photosensitive area | 10 μm max.     | Automated camera  |

# Spectral response (typical example)

KMPDB0369EA

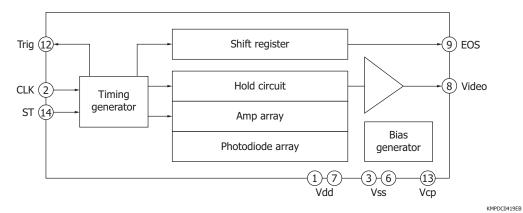

# **Block diagram**

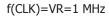

# Output waveforms of one pixel

The timing for acquiring the video signal is synchronized with the rising edge of Trig pulse (See red arrow below.).

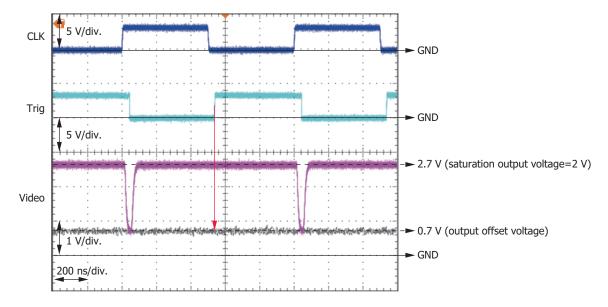

# - Timing chart

| Parameter                       | Symbol           | Min.      | Тур. | Max. | Unit |

|---------------------------------|------------------|-----------|------|------|------|

| Start pulse cycle*13            | tpi(ST)          | 70/f(CLK) | -    | -    | S    |

| Start pulse high period*13 *14  | thp(ST)          | 6/f(CLK)  | -    | -    | S    |

| Start pulse low period          | tlp(ST)          | 64/f(CLK) | -    | -    | S    |

| Start pulse rise and fall times | tr(ST), tf(ST)   | 0         | 10   | 30   | ns   |

| Clock pulse duty ratio          | -                | 45        | 50   | 55   | %    |

| Clock pulse rise and fall times | tr(CLK), tf(CLK) | 0         | 10   | 30   | ns   |

<sup>\*13:</sup> Dark output increases if the start pulse cycle or the start pulse high period is lengthened.

The shift register starts operation at the rising edge of CLK immediately after ST goes low.

The integration time can be changed by changing the ratio of the high and low periods of ST.

If the first Trig pulse after ST goes low is counted as the first pulse, the Video signal is acquired at the rising edge of the 50th Trig pulse.

<sup>\*14:</sup> The integration time equals the high period of ST plus 34 CLK cycles.

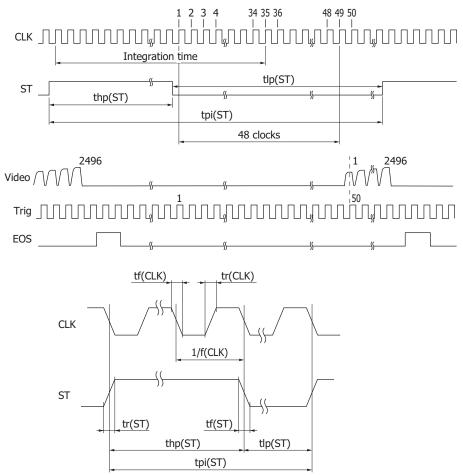

#### Operation example

This example assumes that the clock pulse frequency is maximized (video data rate is also maximized), the time of one scan is minimized, and the integration time is maximized.

Clock pulse frequency = Video data rate = 10 MHz

Start pulse cycle =  $2548/f(CLK) = 2548/10 \text{ MHz} = 254.8 \,\mu\text{s}$

High period of start pulse = Start pulse cycle - Start pulse's low period min.

=  $2548/f(CLK) - 64/f(CLK) = 2548/10 \text{ MHz} - 64/10 \text{ MHz} = 248.4 \mu s$

Integration time is equal to the high period of start pulse + 34 cycles of clock pulses, so it will be  $248.4 + 3.4 = 251.8 \,\mu s$ .

....

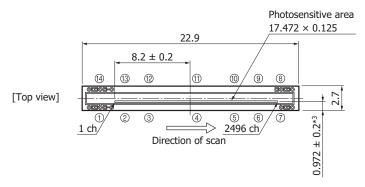

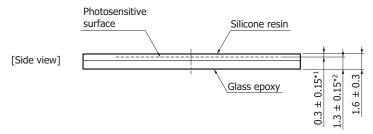

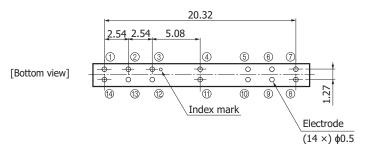

#### - Dimensional outline (unit: mm)

Tolerance unless otherwise noted: ±0.1

- \*1: Distance from package surface to photosensitive surface

- \*2: Distance from package bottom to photosensitive surface

- \*3: Distance from package side surface to center of photosensitive

KMPDA0295EF

### Pin connections

| Pin no. | Symbol | I/O | Description                         |

|---------|--------|-----|-------------------------------------|

| 1       | Vdd    | I   | Supply voltage                      |

| 2       | CLK    | I   | Clock pulse                         |

| 3       | Vss    | -   | GND                                 |

| 4       | NC     | -   | No connection                       |

| 5       | NC     | -   | No connection                       |

| 6       | Vss    | -   | GND                                 |

| 7       | Vdd    | I   | Supply voltage                      |

| 8       | Video  | 0   | Video signal                        |

| 9       | EOS    | 0   | End of scan                         |

| 10      | NC     | -   | No connection                       |

| 11      | NC     | -   | No connection                       |

| 12      | Trig   | 0   | Trigger pulse                       |

| 13      | Vcp    | I   | Bias voltage for booster circuit*15 |

| 14      | ST     | I   | Start pulse                         |

<sup>\*15:</sup> Voltage of approx. 5.5 V, which was boosted by the chip's internal booster circuit, appears at the terminal. To maintain the voltage, insert a capacitor of about 1  $\mu\text{F}$  between GND and Vcp.

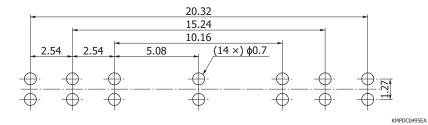

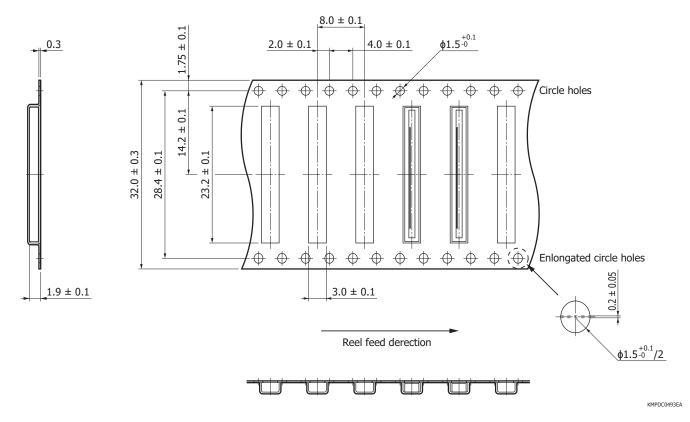

# Recommended land pattern (unit: mm)

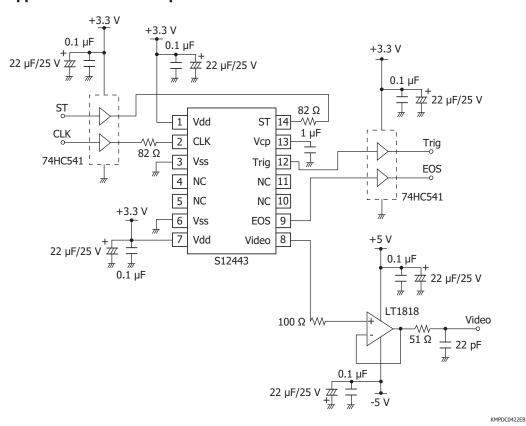

# - Application circuit example

# Standard packing specifications

■ Reel (conforms to JEITA ET-7200)

| Dimensions | Hub diameter | Tape width | Material   | Electrostatic characteristics |

|------------|--------------|------------|------------|-------------------------------|

| 330 mm     | 100 mm       | 32 mm      | Plastic*16 | Conductive                    |

<sup>\*16:</sup> Compound of polyacetylene, polypyrrole, polythiophene and polyaniline

■ Embossed (unit: mm, material: plastic\*16, conductive)

- Packing quantity1000 pcs/reelPacking specifications may vary on orders less than 1000 pieces.

- Packing type

Reel and desiccant in moisture-proof packing (vaccum-sealed)

# - Recommended temperature profile for reflow soldering (typical example)

KMPDB0405EA

- This product supports lead-free soldering. After unpacking, store it in an environment at a temperature of 30 °C or less and a humidity of 60% or less, and perform soldering within 4 weeks.

- The effect that the product receives during reflow soldering varies depending on the circuit board and reflow oven that are used. Before actual reflow soldering, check for any problems by tesiting out the reflow soldering methods in advance.

#### Precautions

# (1) Electrostatic countermeasures

- This device has a built-in protection circuit as a safeguard against static electrical charges. However, to prevent destroying the device with electrostatic charges, take countermeasures such as grounding yourself, the workbench and tools.

- · Protect this device from surge voltages which might be caused by peripheral equipment.

#### (2) Package handling

- The photosensitive area of this device is sealed and protected by transparent resin. When compared to a glass faceplate, the surface of transparent resin may be less uniform and is more likely to be scratched. Be very careful when handling this device and also when designing the optical systems.

- · Dust or grime on the light input window might cause nonuniform sensitivity. To remove dust or grime, blow it off with compressed air.

#### (3) Surface protective tape

· Protective tape is affixed to the surface of this product to protect the photosensitive area. After assembling the product, remove the tape before use.

# **CMOS linear image sensor**

S12443

#### - Related information

www.hamamatsu.com/sp/ssd/doc\_en.html

- Precautions

- · Notice

- · Image sensor / Precautions

- · Surface mount type products / Precautions

- · Resin-sealed CMOS linear image sensors / Precautions

Information described in this material is current as of July, 2014.

Product specifications are subject to change without prior notice due to improvements or other reasons. This document has been carefully prepared and the information contained is believed to be accurate. In rare cases, however, there may be inaccuracies such as text errors. Before using these products, always contact us for the delivery specification sheet to check the latest specifications.

Type numbers of products listed in the delivery specification sheets or supplied as samples may have a suffix "(X)" which means preliminary specifications or a suffix "(Z)" which means developmental specifications.

The product warranty is valid for one year after delivery and is limited to product repair or replacement for defects discovered and reported to us within that one year period. However, even if within the warranty period we accept absolutely no liability for any loss caused by natural disasters or improper product use.

Copying or reprinting the contents described in this material in whole or in part is prohibited without our prior permission.

# **HAMAMATSU**

www.hamamatsu.com

HAMAMATSU PHOTONICS K.K., Solid State Division

1126-1 Ichino-cho, Higashi-ku, Hamamatsu City, 435-8558 Japan, Telephone: (81) 53-434-3311, Fax: (81) 53-434-5184

U.S.A.: Hamamatsu Corporation: 360 Foothill Road, Bridgewater, N.J. 08807, U.S.A., Telephone: (1) 908-231-0960, Fax: (1) 908-231-1218

Germany: Hamamatsu Photonics Deutschland GmbH: Arzbergerstr. 10, D-82211 Herrsching am Ammersee, Germany, Telephone: (49) 8152-375-0, Fax: (49) 8152-265-8

France: Hamamatsu Photonics France S.A.R.L.: 19, Rue du Saule Trapu, Parc du Moulin de Massy, 91882 Massy Cedex, France, Telephone: 33-(1) 69 53 71 00, Fax: 33-(1) 69 53 71 00

United Kingdom: Hamamatsu Photonics UK Limited: 2 Howard Court, 10 Tewin Road, Welwyn Garden City, Hertfordshire AL7 1BW, United Kingdom, Telephone: (44) 1707-294888, Fax: (44) 1707-325777

North Europe: Hamamatsu Photonics Norden AB: Torshamnsgatan 35 16440 Kista, Sweden, Telephone: (36) 02-93581733, Fax: (36) 02-93581731

China: Hamamatsu Photonics (China) Co., Ltd.: B1201, Jiaming Center, No.27 Dongsanhuan Beilu, Chaoyang District, Beijing 100020, China, Telephone: (86) 10-6586-6006, Fax: (86) 1