# **CMOS linear image sensors**

S8377/S8378 series

# **Built-in timing generator and signal process**ing circuit; 5 V single supply operation

The S8377/S8378 series is a family of CMOS linear image sensors designed for image input applications. These linear image sensors operate from 5 V single supply with only start and clock pulse inputs, making them easy to use. The signal processing circuit has a charge amplifier with excellent input/output characteristics and allows signal readout at 500 kHz. The photodiodes of the S8377 series have a height of 0.5 mm and are arrayed in a row at a spacing of 50 µm. The photodiodes of the S8378 series also have a height of 0.5 mm but are arrayed at a spacing of 25 µm. The photodiodes are available in 3 different pixel quantities for each series: 128 (S8377-128Q), 256 (S8377-256Q, S8378-256Q), 512 (S8377-512Q, S8378-512Q) and 1024 (S8378-1024Q). Quartz glass is the standard window material.

#### Features

- → Wide photosensitive area Pixel pitch: 50 µm (S8377 series) 25 µm (S8378 series)

- Pixel height: 0.5 mm

- On-chip charge amplifier with excellent input/output characteristics

- Built-in timing generator allows operation with only start and clock pulse inputs

- Maximum operating clock frequency: 500 kHz

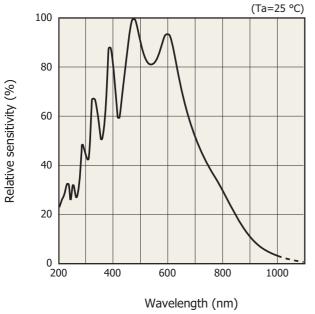

- Spectral response range: 200 to 1000 nm

- 5 V single power supply operation

- 3 8-pin small package, S8377 and S8378 series are pin compatible.

### Applications

- Image input devices

- Optical sensing devices

#### Structure

| Parameter        | S8377-128Q | S8377-256Q | S8377-512Q | S8378-256Q | S8378-512Q | S8378-1024Q | Unit |

|------------------|------------|------------|------------|------------|------------|-------------|------|

| Number of pixels | 128        | 256        | 512        | 256        | 512        | 1024        | -    |

| Pixel pitch      | 50         |            |            |            | μm         |             |      |

| Pixel height     |            | 0.5        |            |            |            |             | mm   |

| Package length   | 15.8       | 22.2       | 35.0       | 15.8       | 22.2       | 35.0        | mm   |

| Number of pins   | 8          |            |            |            |            | -           |      |

| Package          | Ceramic    |            |            |            |            | -           |      |

| Window material  | Quartz     |            |            |            |            | -           |      |

#### Absolute maximum ratings

| Parameter                       | Symbol | Condition | Value       | Unit |

|---------------------------------|--------|-----------|-------------|------|

| Supply voltage                  | Vdd    | Ta=25 °C  | -0.3 to +10 | V    |

| Gain selection terminal voltage | Vg     | Ta=25 °C  | -0.3 to +10 | V    |

| Clock pulse voltage             | V(CLK) | Ta=25 °C  | -0.3 to +10 | V    |

| Start pulse voltage             | V(ST)  | Ta=25 °C  | -0.3 to +10 | V    |

| Operating temperature*1         | Topr   |           | -20 to +60  | °C   |

| Storage temperature*1           | Tstg   |           | -20 to +80  | °C   |

<sup>\*1:</sup> No condensation

Note: Exceeding the absolute maximum ratings even momentarily may cause a drop in product quality. Always be sure to use the product within the absolute maximum ratings.

#### **⇒** Recommended terminal voltage

| Parameter            |            | Symbol | Min.       | Тур. | Max.       | Unit |

|----------------------|------------|--------|------------|------|------------|------|

| Supply voltage       |            | Vdd    | 4.75       | 5    | 5.25       | V    |

| Gain selection       | High gain  | Vg     | 0          | -    | 0.4        | V    |

| terminal voltage     | Low gain   | vy     | Vdd - 0.25 | Vdd  | Vdd + 0.25 | V    |

| LINCK DILISE VOITAGE | High level | V(CLK) | Vdd - 0.25 | Vdd  | Vdd + 0.25 | V    |

|                      | Low level  |        | 0          | -    | 0.4        | V    |

| Start pulse voltage  | High level | V/(CT) | Vdd - 0.25 | Vdd  | Vdd + 0.25 | V    |

|                      | Low level  | V(ST)  | 0          | -    | 0.4        | V    |

#### **Electrical characterisitics**

| Parameter               | Symbol | Min.  | Тур. | Max.  | Unit |

|-------------------------|--------|-------|------|-------|------|

| Clock pulse frequency*2 | f(CLK) | 0.1 k | -    | 500 k | Hz   |

| Output impedance*3      | Zo     | -     | 1    | -     | kΩ   |

| Power consumption       | Р      | -     | 15   | -     | mW   |

<sup>\*2:</sup> Ta=25 °C, Vdd=5 V, V(CLK)=V(ST)=5 V, Vg=5 V (low gain)

Use a JFET or CMOS input, high-impedance input op amp as the buffer amplifier.

#### **■** Electrical and optical characteristics [Ta=25 °C, Vdd=5 V, V(CLK)=V(ST)=5 V]

| Parameter                 |                     | Symbol   | S8377 series |              | S8378 series |             |              | Unit |        |

|---------------------------|---------------------|----------|--------------|--------------|--------------|-------------|--------------|------|--------|

|                           |                     | Syllibol | Min.         | Тур.         | Max.         | Min.        | Тур.         | Max. | Ullit  |

| Spectral response range   |                     | λ        | 200 to 1000  |              |              | 200 to 1000 |              |      | nm     |

| Peak sensitivity waveleng | gth                 | λр       | -            | 500          | -            | -           | 500          | -    | nm     |

| Photosensitivity          | High gain           | S        | -            | 22           | -            | -           | 22           | -    | \/// - |

| FIIOLOSEIISILIVILY        | Low gain            | 3        | -            | 4.4          | -            | -           | 4.4          | -    | V/lx⋅s |

| Dark current              |                     | ID       | -            | 0.01         | 0.03         | -           | 0.01         | 0.03 | рА     |

| Saturation charge         |                     | Qsat     | -            | 12.5         | -            | -           | 6.3          | -    | pC     |

| Feedback capacitance*4    | High gain           | Cf       | -            | 1            | -            | -           | 0.5          | -    |        |

| of charge amplifier       | Low gain            | Cf       | -            | 5            | -            | -           | 2.5          | -    | - pF   |

| Dark output valtage*5     | High gain           | Vd       | -            | 1.0          | 3.0          | -           | 2.0          | 6.0  | mV     |

| Dark output voltage*5     | Low gain            |          | -            | 0.2          | 0.6          | -           | 0.4          | 1.2  |        |

| Caturation output valtage | High gain           | Vsat     | 2.8          | 3.2          | -            | 2.8         | 3.2          | -    | V      |

| Saturation output voltage | Low gain            |          | 2.1          | 2.5          | -            | 2.1         | 2.5          | -    | \ \ \  |

| Caturation oversure*6     | High gain           | Esat     | -            | 145          | -            | -           | 145          | -    | m! c   |

| Saturation exposure*6     | Low gain            | ESdl     | -            | 570          | -            | -           | 570          | -    | mlx⋅s  |

|                           |                     |          | -            | 0.4 (-128Q)  | -            | -           | 0.9 (-256Q)  | -    | mV rms |

|                           | High gain           |          | -            | 0.5 (-256Q)  | -            | -           | 1.3 (-512Q)  | -    |        |

| Readout noise             |                     | Nie      | -            | 0.8 (-512Q)  | -            | -           | 2.1 (-1024Q) | -    |        |

|                           |                     | Nr       | -            | 0.1 (-128Q)  | -            | -           | 0.2 (-256Q)  | -    |        |

|                           | Low gain            | -        | -            | 0.15 (-256Q) | -            | -           | 0.3 (-512Q)  | -    |        |

|                           |                     |          | -            | 0.2 (-512Q)  | -            | -           | 0.4 (-1024Q) | -    |        |

| Photoresponse nonunifor   | rmity* <sup>7</sup> | PRNU     | -            | -            | ±3           | -           | -            | ±3   | %      |

<sup>\*4:</sup> Vg=5 V (low gain), Vg=0 V (high gain)

<sup>\*3:</sup> An increased current consumption at the video terminal rises the sensor chip temperature causing an increased dark current. Connect a buffer amplifier for impedance conversion to the video terminal so that the current flowing to the video terminal is minimized.

<sup>\*5:</sup> Integration time=100 ms

<sup>\*6:</sup> Measured with a tungsten lamp of 2856 K

<sup>\*7:</sup> Photoresponse nonuniformity (PRNU) is the output nonuniformity that occurs when the entire photosensitive area is uniformly illuminated by light which is 50% of the saturation exposure level. PRNU is defined as follows: PRNU= ΔX/X × 100 [%]

X: average output of all pixels,  $\Delta X$ : difference between X and maximum or minimum output

#### Spectral response (typical example)

KMPDB0213EC

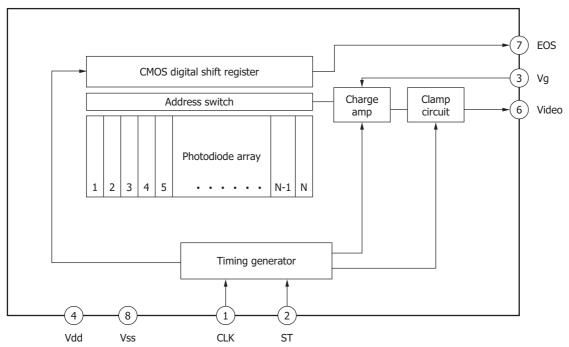

#### **Block diagram**

KMPDC0150EB

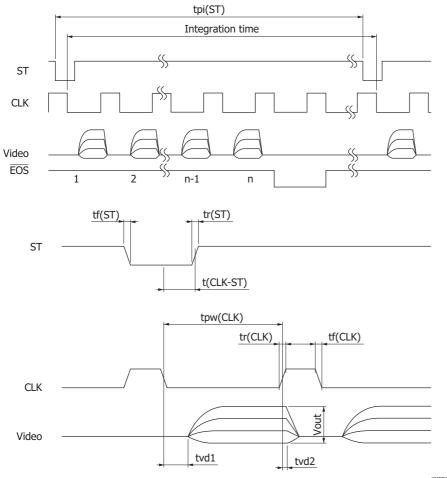

#### Timing chart

| Parameter                       | Symbol           | Min.                                | Тур. | Max. | Unit |

|---------------------------------|------------------|-------------------------------------|------|------|------|

| Start pulse width interval      | tpi(ST)          | $1/f \times$ (number of pixels + 2) | -    | -    | S    |

| Start pulse rise and fall times | tr(ST), tf(ST)   | 0                                   | 20   | 30   | ns   |

| Clock pulse width               | tpw(CLK)         | 1000 ns                             | -    | 5 ms | -    |

| Clock pulse rise and fall times | tr(CLK), tf(CLK) | 0                                   | 20   | 30   | ns   |

| Clock pulse-start pulse timing  | t(CLK-ST)        | 400 ns                              | -    | 5 ms | -    |

| Video delay time 1              | tvd1             | 200                                 | 300  | 400  | ns   |

| Video delay time 2              | tvd2             | 50                                  | 150  | 250  | ns   |

Note: The CLK pulse should be set from high to low just once when the ST pulse is low. The internal shift register starts operating at this timming.

Integration time is determined by the interval between the CLK falling edge during the Low period of a start pulse and the CLK falling edge during the Low period of the next start pulse. However, since the charge integration of each pixel is carried out between the signal readout of that pixel and the next signal readout of the same pixel, the start time of charge integration differs depending on each pixel. In addition, the next start pulse cannot be input until signal readout from all pixels is completed.

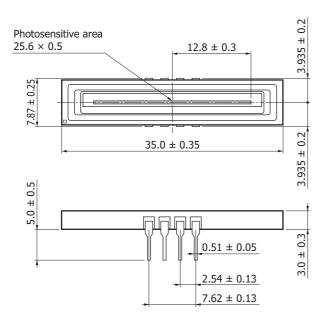

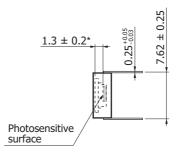

#### Dimensional outlines (unit: mm)

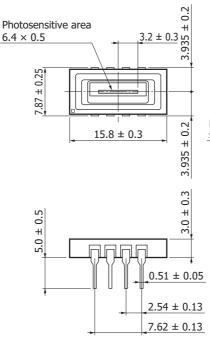

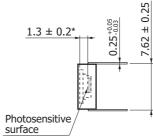

#### S8377-128Q, S8378-256Q

\* Distance from upper surface of window to photosensitive surface

KMPDA0150ED

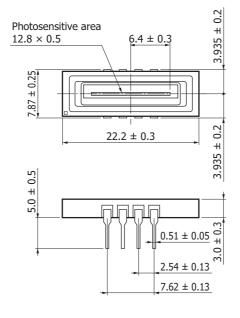

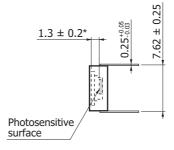

#### S8377-256Q, S8378-512Q

\* Distance from upper surface of window to photosensitive surface

KMPDA0151ED

#### S8377-512Q, S8378-1024Q

\* Distance from upper surface of window to photosensitive surface

KMPDA0152ED

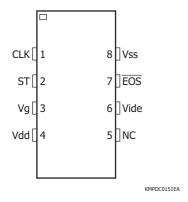

#### **₽** Pin connections

| Pin no. | Symbol | Name of pin            | Function                                                                                                                                                                                                                            |

|---------|--------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | CLK    | Clock pulse            | Pulse input to operate the shift register. The readout time (data rate) equals the clock pulse frequency.                                                                                                                           |

| 2       | ST     | Start pulse            | Starts the shift register operation. Integration time is determined by the interval between the CLK falling edge during the falling period of a start pulse and the CLK falling edge during the Low period of the next start pulse. |

| 3       | Vg     | Gain selection voltage | Input of 5 V selects "Low gain" and 0 V selects "High gain".                                                                                                                                                                        |

| 4       | Vdd    | Supply voltage         | 5 V typ.                                                                                                                                                                                                                            |

| 5       | NC     |                        | Open                                                                                                                                                                                                                                |

| 6       | Video  | Video                  | Signal output. Positive-going output from 1 V                                                                                                                                                                                       |

| 7       | EOS    | End of scan            | Negative-going signal output obtained at a timing following the last pixel scan                                                                                                                                                     |

| 8       | Vss    | Ground                 |                                                                                                                                                                                                                                     |

#### **CMOS linear image sensors**

#### S8377/S8378 series

#### Handling precautions

#### (1) Electrostatic countermeasures

Although the CMOS linear image sensor is protected against static electricity, proper electrostatic countermeasures must be provided to prevent device destruction by static electricity. For example, such measures include wearing non-static gloves and clothes, and grounding the work area and tools.

#### (2) Incident window

If the incident window is contaminated or scratched, the output uniformity will deteriorate considerably, so care should be taken in handling the window. Avoid touching it with bare hands.

The window surface should be cleaned before using the device. If dry cloth or dry cotton swab is used to rub the window surface, static electricity may be generated, and therefore this practice should be avoided. Use soft cloth, cotton swab or soft paper moistened with ethyl alcohol to wipe off dirt and foreign matter on the window surface.

#### (3) UV exposure

The CMOS linear image sensor is designed to suppress performance deterioration due to UV exposure. Even so, avoid unnecessary UV exposure to the device.

Also, be careful not to allow UV light to strike the cemented portion between the ceramic base and the glass.

#### (4) Operating and storage environments

Always observe the rated temperature range when handling the device. Operating or storing the device at an excessively high temperature and humidity may cause variations in performance characteristics and must be avoided.

#### - Related information

www.hamamatsu.com/sp/ssd/doc\_en.html

- Precautions

- Notice

- · Image sensors/Precautions

Information described in this material is current as of February, 2014.

Product specifications are subject to change without prior notice due to improvements or other reasons. This document has been carefully prepared and the information contained is believed to be accurate. In rare cases, however, there may be inaccuracies such as text errors. Before using these products, always contact us for the delivery specification sheet to check the latest specifications.

Type numbers of products listed in the delivery specification sheets or supplied as samples may have a suffix "(X)" which means preliminary specifications or a suffix "(Z)" which means developmental specifications.

The product warranty is valid for one year after delivery and is limited to product repair or replacement for defects discovered and reported to us within that one year period. However, even if within the warranty period we accept absolutely no liability for any loss caused by natural disasters or improper product use.

Copying or reprinting the contents described in this material in whole or in part is prohibited without our prior permission.

## HAMAMATSU

www.hamamatsu.com

HAMAMATSU PHOTONICS K.K., Solid State Division